2次元相補論理回路の垂直3次元集積化における van der Waals 分極工学

Core Concepts

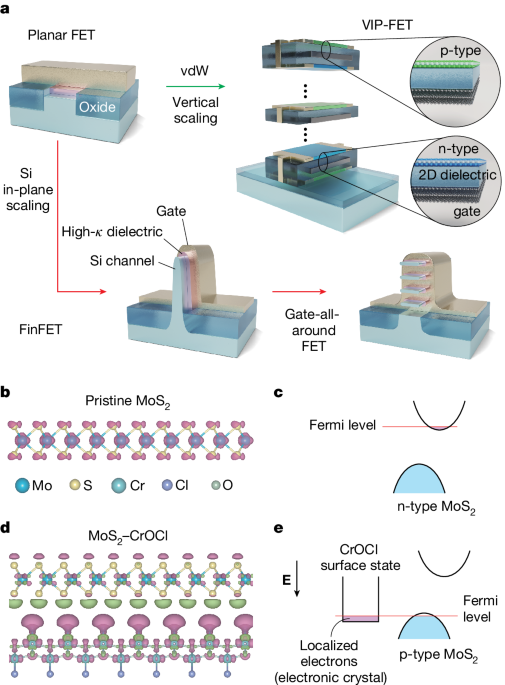

van der Waals 界面結合を利用して2次元MoS2半導体のキャリア極性を n型から p型に再構成し、垂直積層された補完論理回路を実現した。

Abstract

本研究では、2次元半導体であるMoS2を van der Waals 反強磁性絶縁体のCrOCl上に積層することで、MoS2のキャリア極性をn型からp型に再構成することに成功した。この手法により、室温で高い正孔移動度(最大約425 cm2 V−1 s−1)、高いオン/オフ比(最大106)、および1年以上の空気安定性を持つトランジスタを実現した。

さらに、この手法を用いて、6層のvan der Waals 積層によるインバータ、14層のvan der Waals 積層によるNAND回路、および14層のvan der Waals 積層によるSRAMなど、垂直積層された補完論理回路を実現した。

本研究の成果は、2次元半導体のキャリア極性制御に関する一般的な知見を提供し、2次元論理ゲートに基づく将来の3次元垂直集積回路の実現に寄与すると期待される。

Van der Waals polarity-engineered 3D integration of 2D complementary logic - Nature

Stats

MoS2トランジスタの正孔移動度は最大約425 cm2 V−1 s−1に達した。

MoS2トランジスタのオン/オフ比は最大106に達した。

MoS2トランジスタは1年以上の空気安定性を示した。

Quotes

"van der Waals 界面結合を利用して2次元MoS2半導体のキャリア極性をn型からp型に再構成することに成功した。"

"室温で高い正孔移動度(最大約425 cm2 V−1 s−1)、高いオン/オフ比(最大106)、および1年以上の空気安定性を持つトランジスタを実現した。"

"6層のvan der Waals 積層によるインバータ、14層のvan der Waals 積層によるNAND回路、および14層のvan der Waals 積層によるSRAMなど、垂直積層された補完論理回路を実現した。"

Key Insights Distilled From

by Yimeng Guo,J... at www.nature.com 05-29-2024

https://www.nature.com/articles/s41586-024-07438-5

Deeper Inquiries

2次元半導体以外の材料を用いた場合、同様の手法で補完論理回路を実現できるだろうか。

本研究で使用された手法は、遷移金属ジカルコゲナイド(TMD)とvan der Waals(vdW)相互作用を利用して、2次元半導体のキャリア極性を制御するものである。この手法は、TMDとvdW結合した材料によって、2次元半導体のキャリア極性を簡単に再構成することが可能であることを示しています。このアプローチは、他の材料にも適用可能であり、例えば異種積層構造や異なるキャリアタイプを持つ2次元層にも適用できる可能性があります。したがって、2次元半導体以外の材料を使用しても、同様の手法を用いて補完論理回路を実現することができる可能性があります。

本手法では、p型ドーピングが安定に実現できているが、n型ドーピングの安定性はどうか。

本研究では、遷移金属ジカルコゲナイド(TMD)をvan der Waals(vdW)反強磁性絶縁体であるクロムオキシクロライド(CrOCl)の上に配置することで、MoS2などの2次元半導体のキャリア極性をn型からp型に容易に再構成できることが示されています。この手法により、室温でホール移動度が約425 cm2 V−1 s−1に達し、オン/オフ比が106に達し、1年以上の安定性を持つトランジスタが実現されています。この結果から、p型ドーピングの安定性は高いと言えます。一方、n型ドーピングの安定性については、本研究では明確な記載がないため、今後の研究でさらなる検証が必要とされるでしょう。

本研究で実現した垂直積層回路の消費電力特性はどのようなものか。

本研究で実現した垂直積層回路は、2次元半導体を用いた補完論理回路で構成されています。これらの回路は、van der Waals(vdW)相互作用を利用して2次元半導体のキャリア極性を制御し、p型およびn型の半導体チャネルを実現しています。これにより、高性能なトランジスタが構築され、消費電力特性が向上しています。具体的には、本研究で実現された垂直積層回路は、低消費電力でありながら高い性能を持つことが示されています。さらに、補完論理回路の構築において、エネルギー効率や消費電力の最適化が重要であり、本研究で示された手法はその向上に貢献する可能性があります。

0