insight - Quantum Computing - # Heterogeneous Integration of Spin-Photon Interfaces in CMOS Quantum System-on-Chip

Scalable Quantum System-on-Chip Architecture Integrating Spin-Photon Interfaces with CMOS Platform

Core Concepts

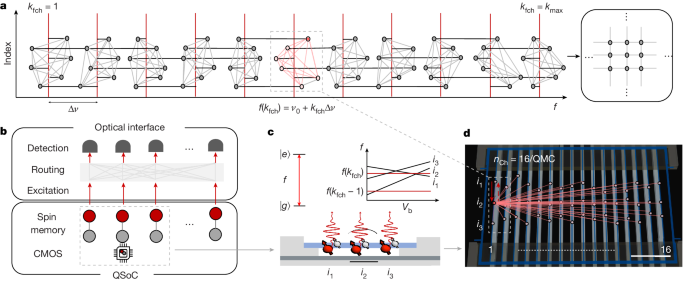

A modular quantum system-on-chip (QSoC) architecture that integrates thousands of individually addressable tin-vacancy spin qubits into an application-specific integrated circuit for scalable quantum computing.

Abstract

The content describes a novel quantum system-on-chip (QSoC) architecture that aims to address the scalability challenge in quantum computing. Key highlights:

The QSoC integrates thousands of individually addressable tin-vacancy spin qubits in two-dimensional arrays of quantum microchiplets into a CMOS-compatible application-specific integrated circuit (ASIC) designed for cryogenic control.

The authors demonstrate crucial fabrication steps and architectural subcomponents, including:

QSoC transfer using a 'lock-and-release' method for large-scale heterogeneous integration

High-throughput spin-qubit calibration and spectral tuning

Efficient spin state preparation and measurement

The QSoC architecture supports full connectivity for quantum memory arrays by spectral tuning across spin-photon frequency channels.

Design studies indicate further scaling potential through increased qubit density, larger QSoC active regions, and optical networking across QSoC modules.

Heterogeneous integration of spin–photon interfaces with a CMOS platform - Nature

Stats

The content does not provide specific numerical data or metrics, but rather focuses on describing the overall QSoC architecture and its key capabilities.

Quotes

"Blueprint studies3,4,5 indicate that general-purpose quantum computing using local quantum communication networks will require millions of physical qubits to encode thousands of logical qubits, presenting an open scalability challenge."

"This QSoC architecture supports full connectivity for quantum memory arrays by spectral tuning across spin–photon frequency channels."

Key Insights Distilled From

by Linsen Li,Lo... at www.nature.com 05-29-2024

https://www.nature.com/articles/s41586-024-07371-7

Deeper Inquiries

What are the key technical challenges in achieving the proposed scaling of the QSoC architecture, and what are the potential solutions being explored?

Achieving scalability in the QSoC architecture poses several technical challenges, such as maintaining qubit coherence across a large array, minimizing crosstalk between qubits, and ensuring efficient qubit control and readout. To address these challenges, potential solutions being explored include implementing error correction codes to enhance qubit coherence, developing advanced qubit control techniques to reduce crosstalk, and optimizing the readout mechanisms for high-throughput operations. Additionally, advancements in material science for improving qubit coherence times and engineering techniques for precise qubit placement are being investigated to enable the scaling of the QSoC architecture.

How does the performance and scalability of the QSoC approach compare to other leading quantum computing architectures, such as superconducting or trapped-ion qubits?

The QSoC approach offers unique advantages in terms of performance and scalability compared to other quantum computing architectures. By integrating thousands of individually addressable tin-vacancy spin qubits in two-dimensional arrays, the QSoC architecture enables high qubit density and full connectivity for quantum memory arrays. This design allows for efficient spin state preparation, measurement, and spectral tuning across spin-photon frequency channels, enhancing the overall performance of the system. In terms of scalability, the modular nature of the QSoC architecture facilitates the integration of larger QSoC active regions and optical networking across modules, paving the way for significant scalability potential. These features position the QSoC approach as a promising candidate for large-scale quantum computing applications.

How can the integration of spin-photon interfaces with CMOS platforms enable the development of hybrid quantum-classical computing systems, and what are the potential applications of such systems?

The integration of spin-photon interfaces with CMOS platforms opens up possibilities for developing hybrid quantum-classical computing systems that leverage the strengths of both quantum and classical technologies. By combining spin qubits with photon interfaces on a CMOS platform, it becomes feasible to perform quantum operations while utilizing classical processing power for control and readout tasks. This hybrid approach can enhance the overall computational capabilities by harnessing the quantum advantages of spin qubits and the classical processing power of CMOS circuits. Potential applications of such systems include quantum error correction, optimization algorithms, and quantum simulations, where the hybrid architecture can offer improved performance and efficiency compared to purely classical or quantum systems.

0